三。SHIELDING的设计方法:

1.绘制PAD层:

在PAD层上根据结构工程师给出的屏蔽架边框进行绘制(宽度一般为0.7mm或0.8mm)。

图形必须为一个封闭的多边形(非常重要)

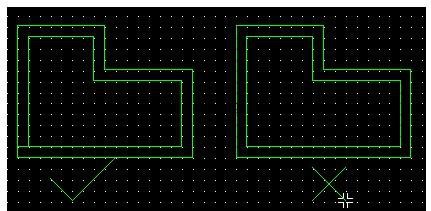

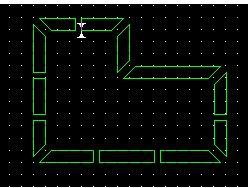

如下图,左边的画法是正确的,右边的画法是错误的。 本文来自www.eadianqi.com

自动控制网www.eadianqi.com版权所有

2.绘制SOLDER MASK层: 自动控制网www.eadianqi.com版权所有

自动控制网www.eadianqi.com版权所有 自动控制网www.eadianqi.com版权所有

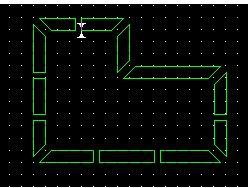

在SOLDER_MASK层上绘制。根据屏蔽架形状画出若干块分割开来的露铜区域(注意拐角处的绘制方法),两块露铜之间的间距为0.2mm,露铜的宽度同PAD的宽度。

3.绘制PASTE_MASK层:

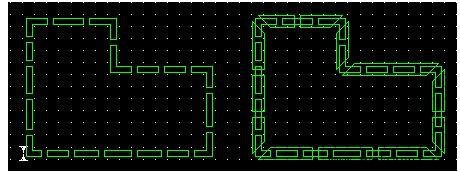

在PASTE_MASK层上绘制。根据屏蔽架形状画出若干块上锡膏的区域,两块PASTE MASK的间距为0.4mm,宽度较PAD单边内缩0.1mm.

注,两块SOLDER MASK之间的空隙处需要有PASTE MASK盖在上面。

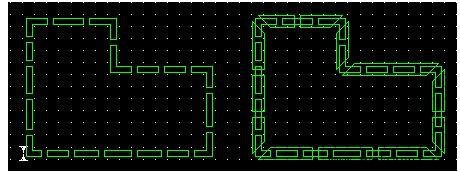

如下图所示,左边为PASTE MASK层,右边为PASTE与SOLDER层叠在一起的效果:

4.基准点放在PAD的一角处。 本文来自www.eadianqi.com

本文来自www.eadianqi.com 本文来自www.eadianqi.com

5.五层边框的尺寸:

Placement_outline尺寸以PAD的最外面边框为准。

Component_body_outline较Place层内缩0.1mm.

Plan_equipement层与Silkscreen层尺寸相同,形状较外边框内缩至PAD的中心处。。

Tolerance层尺寸同Placement_outline.

这五层的属性和线宽设置与前面介绍的方法相同。

6.屏蔽架封装其他部分的做法与前面介绍的封装做法相同。

|

本文来自www.eadianqi.com

本文来自www.eadianqi.com